公開方法(Public Methods) | |

| virtual | ~MRCC (void) override |

| Destroy the object. | |

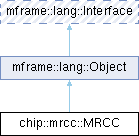

公開方法(Public Methods) 繼承自 mframe::lang::Object 公開方法(Public Methods) 繼承自 mframe::lang::Object | |

| Object (void) | |

| Construct a new Object object. | |

| virtual | ~Object (void) override |

| Destroy the Object object. | |

| void * | operator new (size_t n) |

| void * | operator new (size_t n, void *p) |

| mframe::lang::Object & | getObject (void) override |

| 取得類Object | |

| void | delay (int milliseconds) const |

| 函數 delay 等待內核滴答中指定的時間段。 對於1的值,系統等待直到下一個計時器滴答發生。 實際時間延遲最多可能比指定時間少一個計時器滴答聲,即在下一個系統滴答聲發生之前立即調用 osDelay(1),線程會立即重新安排。 | |

| bool | equals (Object *object) const |

| 函數 delay 等待內核滴答中指定的時間段。 對於1的值,系統等待直到下一個計時器滴答發生。 實際時間延遲最多可能比指定時間少一個計時器滴答聲,即在下一個系統滴答聲發生之前立即調用 osDelay(1),線程會立即重新安排。 | |

| bool | equals (Object &object) const |

| 函數 delay 等待內核滴答中指定的時間段。 對於1的值,系統等待直到下一個計時器滴答發生。 實際時間延遲最多可能比指定時間少一個計時器滴答聲,即在下一個系統滴答聲發生之前立即調用 osDelay(1),線程會立即重新安排。 | |

| void | wait (void) const |

| 導致當前線程等待,直到另一個線程調用此對象的notify()方法或notifyAll()方法,或指定的時間 已過。 | |

| bool | wait (int timeout) const |

| 導致當前線程等待,直到另一個線程調用此對象的 notify()方法或 notifyAll()方法,或其他一些線 程中斷當前線程,或一定量的實時時間。 | |

| bool | yield (void) const |

| 函數yield()將控制權傳遞給處於READY狀態且具有相同優先級的下一個線程。 如果在READY狀態下沒有其他優先級相同的線程,則當前線程繼續執行,不會發生線程切換。 | |

| int | lock (void) const |

| 核心鎖定,在調用unlock以前將不會進行執行緒切換 | |

| int | unlock (void) const |

| 核心解鎖。 | |

| mframe::sys::Thread * | currentThread (void) const |

| 取得當前的執行緒 | |

| virtual int | hashcode (void) const |

| 返回對象的哈希碼值。支持這種方法是為了散列表,如HashMap提供的那樣。 | |

公開方法(Public Methods) 繼承自 mframe::lang::Interface 公開方法(Public Methods) 繼承自 mframe::lang::Interface | |

| virtual | ~Interface (void)=default |

| Destroy the struct object. | |

靜態公開方法(Static Public Methods) | |

| static constexpr uint32 | GLB_RST0_INPUTMUX0 (uint32 value) |

| MRCC_GLB_RST0 - INPUTMUX0. | |

| static constexpr uint32 | GLB_RST0_I3C0 (uint32 value) |

| MRCC_GLB_RST0 - I3C0. | |

| static constexpr uint32 | GLB_RST0_CTIMER0 (uint32 value) |

| MRCC_GLB_RST0 - CTIMER0. | |

| static constexpr uint32 | GLB_RST0_CTIMER1 (uint32 value) |

| MRCC_GLB_RST0 - CTIMER1. | |

| static constexpr uint32 | GLB_RST0_CTIMER2 (uint32 value) |

| MRCC_GLB_RST0 - CTIMER2. | |

| static constexpr uint32 | GLB_RST0_CTIMER3 (uint32 value) |

| MRCC_GLB_RST0 - CTIMER3. | |

| static constexpr uint32 | GLB_RST0_CTIMER4 (uint32 value) |

| MRCC_GLB_RST0 - CTIMER4. | |

| static constexpr uint32 | GLB_RST0_FREQME (uint32 value) |

| MRCC_GLB_RST0 - FREQME. | |

| static constexpr uint32 | GLB_RST0_UTICK0 (uint32 value) |

| MRCC_GLB_RST0 - UTICK0. | |

| static constexpr uint32 | GLB_RST0_DMA (uint32 value) |

| MRCC_GLB_RST0 - DMA. | |

| static constexpr uint32 | GLB_RST0_AOI0 (uint32 value) |

| MRCC_GLB_RST0 - AOI0. | |

| static constexpr uint32 | GLB_RST0_CRC0 (uint32 value) |

| MRCC_GLB_RST0 - CRC0. | |

| static constexpr uint32 | GLB_RST0_EIM0 (uint32 value) |

| MRCC_GLB_RST0 - EIM0. | |

| static constexpr uint32 | GLB_RST0_ERM0 (uint32 value) |

| MRCC_GLB_RST0 - ERM0. | |

| static constexpr uint32 | GLB_RST0_AOI1 (uint32 value) |

| MRCC_GLB_RST0 - AOI1. | |

| static constexpr uint32 | GLB_RST0_FLEXIO0 (uint32 value) |

| MRCC_GLB_RST0 - FLEXIO0. | |

| static constexpr uint32 | GLB_RST0_LPI2C0 (uint32 value) |

| MRCC_GLB_RST0 - LPI2C0. | |

| static constexpr uint32 | GLB_RST0_LPI2C1 (uint32 value) |

| MRCC_GLB_RST0 - LPI2C1. | |

| static constexpr uint32 | GLB_RST0_LPSPI0 (uint32 value) |

| MRCC_GLB_RST0 - LPSPI0. | |

| static constexpr uint32 | GLB_RST0_LPSPI1 (uint32 value) |

| MRCC_GLB_RST0 - LPSPI1. | |

| static constexpr uint32 | GLB_RST0_LPUART0 (uint32 value) |

| MRCC_GLB_RST0 - LPUART0. | |

| static constexpr uint32 | GLB_RST0_LPUART1 (uint32 value) |

| MRCC_GLB_RST0 - LPUART1. | |

| static constexpr uint32 | GLB_RST0_LPUART2 (uint32 value) |

| MRCC_GLB_RST0 - LPUART2. | |

| static constexpr uint32 | GLB_RST0_LPUART3 (uint32 value) |

| MRCC_GLB_RST0 - LPUART3. | |

| static constexpr uint32 | GLB_RST0_LPUART4 (uint32 value) |

| MRCC_GLB_RST0 - LPUART4. | |

| static constexpr uint32 | GLB_RST0_USB0 (uint32 value) |

| MRCC_GLB_RST0 - USB0. | |

| static constexpr uint32 | GLB_RST0_QDC0 (uint32 value) |

| MRCC_GLB_RST0 - QDC0. | |

| static constexpr uint32 | GLB_RST0_QDC1 (uint32 value) |

| MRCC_GLB_RST0 - QDC1. | |

| static constexpr uint32 | GLB_RST0_FLEXPWM0 (uint32 value) |

| MRCC_GLB_RST0 - FLEXPWM0. | |

| static constexpr uint32 | GLB_RST0_FLEXPWM1 (uint32 value) |

| MRCC_GLB_RST0 - FLEXPWM1. | |

| static constexpr uint32 | GLB_RST0_SET_DATA (uint32 value) |

| MRCC_GLB_RST0_SET - DATA. | |

| static constexpr uint32 | GLB_RST0_CLR_DATA (uint32 value) |

| MRCC_GLB_RST0_CLR - DATA. | |

| static constexpr uint32 | GLB_RST1_OSTIMER0 (uint32 value) |

| MRCC_GLB_RST1 - OSTIMER0. | |

| static constexpr uint32 | GLB_RST1_ADC0 (uint32 value) |

| MRCC_GLB_RST1 - ADC0. | |

| static constexpr uint32 | GLB_RST1_ADC1 (uint32 value) |

| MRCC_GLB_RST1 - ADC1. | |

| static constexpr uint32 | GLB_RST1_CMP1 (uint32 value) |

| MRCC_GLB_RST1 - CMP1. | |

| static constexpr uint32 | GLB_RST1_DAC0 (uint32 value) |

| MRCC_GLB_RST1 - DAC0. | |

| static constexpr uint32 | GLB_RST1_OPAMP0 (uint32 value) |

| MRCC_GLB_RST1 - OPAMP0. | |

| static constexpr uint32 | GLB_RST1_PORT0 (uint32 value) |

| MRCC_GLB_RST1 - PORT0. | |

| static constexpr uint32 | GLB_RST1_PORT1 (uint32 value) |

| MRCC_GLB_RST1 - PORT1. | |

| static constexpr uint32 | GLB_RST1_PORT2 (uint32 value) |

| MRCC_GLB_RST1 - PORT2. | |

| static constexpr uint32 | GLB_RST1_PORT3 (uint32 value) |

| MRCC_GLB_RST1 - PORT3. | |

| static constexpr uint32 | GLB_RST1_PORT4 (uint32 value) |

| MRCC_GLB_RST1 - PORT4. | |

| static constexpr uint32 | GLB_RST1_FLEXCAN0 (uint32 value) |

| MRCC_GLB_RST1 - FLEXCAN0. | |

| static constexpr uint32 | GLB_RST1_LPI2C2 (uint32 value) |

| MRCC_GLB_RST1 - LPI2C2. | |

| static constexpr uint32 | GLB_RST1_LPI2C3 (uint32 value) |

| MRCC_GLB_RST1 - LPI2C3. | |

| static constexpr uint32 | GLB_RST1_GPIO0 (uint32 value) |

| MRCC_GLB_RST1 - GPIO0. | |

| static constexpr uint32 | GLB_RST1_GPIO1 (uint32 value) |

| MRCC_GLB_RST1 - GPIO1. | |

| static constexpr uint32 | GLB_RST1_GPIO2 (uint32 value) |

| MRCC_GLB_RST1 - GPIO2. | |

| static constexpr uint32 | GLB_RST1_GPIO3 (uint32 value) |

| MRCC_GLB_RST1 - GPIO3. | |

| static constexpr uint32 | GLB_RST1_GPIO4 (uint32 value) |

| MRCC_GLB_RST1 - GPIO4. | |

| static constexpr uint32 | GLB_RST1_SET_DATA (uint32 value) |

| MRCC_GLB_RST1_SET - DATA. | |

| static constexpr uint32 | GLB_RST1_CLR_DATA (uint32 value) |

| MRCC_GLB_RST1_CLR - DATA. | |

| static constexpr uint32 | GLB_CC0_INPUTMUX0 (uint32 value) |

| MRCC_GLB_CC0 - INPUTMUX0. | |

| static constexpr uint32 | GLB_CC0_I3C0 (uint32 value) |

| MRCC_GLB_CC0 - I3C0. | |

| static constexpr uint32 | GLB_CC0_CTIMER0 (uint32 value) |

| MRCC_GLB_CC0 - CTIMER0. | |

| static constexpr uint32 | GLB_CC0_CTIMER1 (uint32 value) |

| MRCC_GLB_CC0 - CTIMER1. | |

| static constexpr uint32 | GLB_CC0_CTIMER2 (uint32 value) |

| MRCC_GLB_CC0 - CTIMER2. | |

| static constexpr uint32 | GLB_CC0_CTIMER3 (uint32 value) |

| MRCC_GLB_CC0 - CTIMER3. | |

| static constexpr uint32 | GLB_CC0_CTIMER4 (uint32 value) |

| MRCC_GLB_CC0 - CTIMER4. | |

| static constexpr uint32 | GLB_CC0_FREQME (uint32 value) |

| MRCC_GLB_CC0 - FREQME. | |

| static constexpr uint32 | GLB_CC0_UTICK0 (uint32 value) |

| MRCC_GLB_CC0 - UTICK0. | |

| static constexpr uint32 | GLB_CC0_WWDT0 (uint32 value) |

| MRCC_GLB_CC0 - WWDT0. | |

| static constexpr uint32 | GLB_CC0_DMA (uint32 value) |

| MRCC_GLB_CC0 - DMA. | |

| static constexpr uint32 | GLB_CC0_AOI0 (uint32 value) |

| MRCC_GLB_CC0 - AOI0. | |

| static constexpr uint32 | GLB_CC0_CRC0 (uint32 value) |

| MRCC_GLB_CC0 - CRC0. | |

| static constexpr uint32 | GLB_CC0_EIM0 (uint32 value) |

| MRCC_GLB_CC0 - EIM0. | |

| static constexpr uint32 | GLB_CC0_ERM0 (uint32 value) |

| MRCC_GLB_CC0 - ERM0. | |

| static constexpr uint32 | GLB_CC0_FMC (uint32 value) |

| MRCC_GLB_CC0 - FMC. | |

| static constexpr uint32 | GLB_CC0_AOI1 (uint32 value) |

| MRCC_GLB_CC0 - AOI1. | |

| static constexpr uint32 | GLB_CC0_FLEXIO0 (uint32 value) |

| MRCC_GLB_CC0 - FLEXIO0. | |

| static constexpr uint32 | GLB_CC0_LPI2C0 (uint32 value) |

| MRCC_GLB_CC0 - LPI2C0. | |

| static constexpr uint32 | GLB_CC0_LPI2C1 (uint32 value) |

| MRCC_GLB_CC0 - LPI2C1. | |

| static constexpr uint32 | GLB_CC0_LPSPI0 (uint32 value) |

| MRCC_GLB_CC0 - LPSPI0. | |

| static constexpr uint32 | GLB_CC0_LPSPI1 (uint32 value) |

| MRCC_GLB_CC0 - LPSPI1. | |

| static constexpr uint32 | GLB_CC0_LPUART0 (uint32 value) |

| MRCC_GLB_CC0 - LPUART0. | |

| static constexpr uint32 | GLB_CC0_LPUART1 (uint32 value) |

| MRCC_GLB_CC0 - LPUART1. | |

| static constexpr uint32 | GLB_CC0_LPUART2 (uint32 value) |

| MRCC_GLB_CC0 - LPUART2. | |

| static constexpr uint32 | GLB_CC0_LPUART3 (uint32 value) |

| MRCC_GLB_CC0 - LPUART3. | |

| static constexpr uint32 | GLB_CC0_LPUART4 (uint32 value) |

| MRCC_GLB_CC0 - LPUART4. | |

| static constexpr uint32 | GLB_CC0_USB0 (uint32 value) |

| MRCC_GLB_CC0 - USB0. | |

| static constexpr uint32 | GLB_CC0_QDC0 (uint32 value) |

| MRCC_GLB_CC0 - QDC0. | |

| static constexpr uint32 | GLB_CC0_QDC1 (uint32 value) |

| MRCC_GLB_CC0 - QDC1. | |

| static constexpr uint32 | GLB_CC0_FLEXPWM0 (uint32 value) |

| MRCC_GLB_CC0 - FLEXPWM0. | |

| static constexpr uint32 | GLB_CC0_FLEXPWM1 (uint32 value) |

| MRCC_GLB_CC0 - FLEXPWM1. | |

| static constexpr uint32 | GLB_CC0_SET_DATA (uint32 value) |

| MRCC_GLB_CC0_SET - DATA. | |

| static constexpr uint32 | GLB_CC0_CLR_DATA (uint32 value) |

| MRCC_GLB_CC0_CLR - DATA. | |

| static constexpr uint32 | GLB_CC1_OSTIMER0 (uint32 value) |

| MRCC_GLB_CC1 - OSTIMER0. | |

| static constexpr uint32 | GLB_CC1_ADC0 (uint32 value) |

| MRCC_GLB_CC1 - ADC0. | |

| static constexpr uint32 | GLB_CC1_ADC1 (uint32 value) |

| MRCC_GLB_CC1 - ADC1. | |

| static constexpr uint32 | GLB_CC1_CMP0 (uint32 value) |

| MRCC_GLB_CC1 - CMP0. | |

| static constexpr uint32 | GLB_CC1_CMP1 (uint32 value) |

| MRCC_GLB_CC1 - CMP1. | |

| static constexpr uint32 | GLB_CC1_DAC0 (uint32 value) |

| MRCC_GLB_CC1 - DAC0. | |

| static constexpr uint32 | GLB_CC1_OPAMP0 (uint32 value) |

| MRCC_GLB_CC1 - OPAMP0. | |

| static constexpr uint32 | GLB_CC1_PORT0 (uint32 value) |

| MRCC_GLB_CC1 - PORT0. | |

| static constexpr uint32 | GLB_CC1_PORT1 (uint32 value) |

| MRCC_GLB_CC1 - PORT1. | |

| static constexpr uint32 | GLB_CC1_PORT2 (uint32 value) |

| MRCC_GLB_CC1 - PORT2. | |

| static constexpr uint32 | GLB_CC1_PORT3 (uint32 value) |

| MRCC_GLB_CC1 - PORT3. | |

| static constexpr uint32 | GLB_CC1_PORT4 (uint32 value) |

| MRCC_GLB_CC1 - PORT4. | |

| static constexpr uint32 | GLB_CC1_FLEXCAN0 (uint32 value) |

| MRCC_GLB_CC1 - FLEXCAN0. | |

| static constexpr uint32 | GLB_CC1_LPI2C2 (uint32 value) |

| MRCC_GLB_CC1 - LPI2C2. | |

| static constexpr uint32 | GLB_CC1_LPI2C3 (uint32 value) |

| MRCC_GLB_CC1 - LPI2C3. | |

| static constexpr uint32 | GLB_CC1_RAMA (uint32 value) |

| MRCC_GLB_CC1 - RAMA. | |

| static constexpr uint32 | GLB_CC1_RAMB (uint32 value) |

| MRCC_GLB_CC1 - RAMB. | |

| static constexpr uint32 | GLB_CC1_GPIO0 (uint32 value) |

| MRCC_GLB_CC1 - GPIO0. | |

| static constexpr uint32 | GLB_CC1_GPIO1 (uint32 value) |

| MRCC_GLB_CC1 - GPIO1. | |

| static constexpr uint32 | GLB_CC1_GPIO2 (uint32 value) |

| MRCC_GLB_CC1 - GPIO2. | |

| static constexpr uint32 | GLB_CC1_GPIO3 (uint32 value) |

| MRCC_GLB_CC1 - GPIO3. | |

| static constexpr uint32 | GLB_CC1_GPIO4 (uint32 value) |

| MRCC_GLB_CC1 - GPIO4. | |

| static constexpr uint32 | GLB_CC1_ROMC (uint32 value) |

| MRCC_GLB_CC1 - ROMC. | |

| static constexpr uint32 | GLB_CC_SET_DATA (uint32 value) |

| MRCC_GLB_CC_SET - DATA. | |

| static constexpr uint32 | GLB_CC_CLR_DATA (uint32 value) |

| MRCC_GLB_CC_CLR - DATA. | |

| static constexpr uint32 | GLB_ACC0_INPUTMUX0 (uint32 value) |

| MRCC_GLB_ACC0 - INPUTMUX0. | |

| static constexpr uint32 | GLB_ACC0_I3C0 (uint32 value) |

| MRCC_GLB_ACC0 - I3C0. | |

| static constexpr uint32 | GLB_ACC0_CTIMER0 (uint32 value) |

| MRCC_GLB_ACC0 - CTIMER0. | |

| static constexpr uint32 | GLB_ACC0_CTIMER1 (uint32 value) |

| MRCC_GLB_ACC0 - CTIMER1. | |

| static constexpr uint32 | GLB_ACC0_CTIMER2 (uint32 value) |

| MRCC_GLB_ACC0 - CTIMER2. | |

| static constexpr uint32 | GLB_ACC0_CTIMER3 (uint32 value) |

| MRCC_GLB_ACC0 - CTIMER3. | |

| static constexpr uint32 | GLB_ACC0_CTIMER4 (uint32 value) |

| MRCC_GLB_ACC0 - CTIMER4. | |

| static constexpr uint32 | GLB_ACC0_FREQME (uint32 value) |

| MRCC_GLB_ACC0 - FREQME. | |

| static constexpr uint32 | GLB_ACC0_UTICK0 (uint32 value) |

| MRCC_GLB_ACC0 - UTICK0. | |

| static constexpr uint32 | GLB_ACC0_WWDT0 (uint32 value) |

| MRCC_GLB_ACC0 - WWDT0. | |

| static constexpr uint32 | GLB_ACC0_DMA (uint32 value) |

| MRCC_GLB_ACC0 - DMA. | |

| static constexpr uint32 | GLB_ACC0_AOI0 (uint32 value) |

| MRCC_GLB_ACC0 - AOI0. | |

| static constexpr uint32 | GLB_ACC0_CRC0 (uint32 value) |

| MRCC_GLB_ACC0 - CRC0. | |

| static constexpr uint32 | GLB_ACC0_EIM0 (uint32 value) |

| MRCC_GLB_ACC0 - EIM0. | |

| static constexpr uint32 | GLB_ACC0_ERM0 (uint32 value) |

| MRCC_GLB_ACC0 - ERM0. | |

| static constexpr uint32 | GLB_ACC0_FMC (uint32 value) |

| MRCC_GLB_ACC0 - FMC. | |

| static constexpr uint32 | GLB_ACC0_AOI1 (uint32 value) |

| MRCC_GLB_ACC0 - AOI1. | |

| static constexpr uint32 | GLB_ACC0_FLEXIO0 (uint32 value) |

| MRCC_GLB_ACC0 - FLEXIO0. | |

| static constexpr uint32 | GLB_ACC0_LPI2C0 (uint32 value) |

| MRCC_GLB_ACC0 - LPI2C0. | |

| static constexpr uint32 | GLB_ACC0_LPI2C1 (uint32 value) |

| MRCC_GLB_ACC0 - LPI2C1. | |

| static constexpr uint32 | GLB_ACC0_LPSPI0 (uint32 value) |

| MRCC_GLB_ACC0 - LPSPI0. | |

| static constexpr uint32 | GLB_ACC0_LPSPI1 (uint32 value) |

| MRCC_GLB_ACC0 - LPSPI1. | |

| static constexpr uint32 | GLB_ACC0_LPUART0 (uint32 value) |

| MRCC_GLB_ACC0 - LPUART0. | |

| static constexpr uint32 | GLB_ACC0_LPUART1 (uint32 value) |

| MRCC_GLB_ACC0 - LPUART1. | |

| static constexpr uint32 | GLB_ACC0_LPUART2 (uint32 value) |

| MRCC_GLB_ACC0 - LPUART2. | |

| static constexpr uint32 | GLB_ACC0_LPUART3 (uint32 value) |

| MRCC_GLB_ACC0 - LPUART3. | |

| static constexpr uint32 | GLB_ACC0_LPUART4 (uint32 value) |

| MRCC_GLB_ACC0 - LPUART4. | |

| static constexpr uint32 | GLB_ACC0_USB0 (uint32 value) |

| MRCC_GLB_ACC0 - USB0. | |

| static constexpr uint32 | GLB_ACC0_QDC0 (uint32 value) |

| MRCC_GLB_ACC0 - QDC0. | |

| static constexpr uint32 | GLB_ACC0_QDC1 (uint32 value) |

| MRCC_GLB_ACC0 - QDC1. | |

| static constexpr uint32 | GLB_ACC0_FLEXPWM0 (uint32 value) |

| MRCC_GLB_ACC0 - FLEXPWM0. | |

| static constexpr uint32 | GLB_ACC0_FLEXPWM1 (uint32 value) |

| MRCC_GLB_ACC0 - FLEXPWM1. | |

| static constexpr uint32 | GLB_ACC1_OSTIMER0 (uint32 value) |

| MRCC_GLB_ACC1 - OSTIMER0. | |

| static constexpr uint32 | GLB_ACC1_ADC0 (uint32 value) |

| MRCC_GLB_ACC1 - ADC0. | |

| static constexpr uint32 | GLB_ACC1_ADC1 (uint32 value) |

| MRCC_GLB_ACC1 - ADC1. | |

| static constexpr uint32 | GLB_ACC1_CMP0 (uint32 value) |

| MRCC_GLB_ACC1 - CMP0. | |

| static constexpr uint32 | GLB_ACC1_CMP1 (uint32 value) |

| MRCC_GLB_ACC1 - CMP1. | |

| static constexpr uint32 | GLB_ACC1_DAC0 (uint32 value) |

| MRCC_GLB_ACC1 - DAC0. | |

| static constexpr uint32 | GLB_ACC1_OPAMP0 (uint32 value) |

| MRCC_GLB_ACC1 - OPAMP0. | |

| static constexpr uint32 | GLB_ACC1_PORT0 (uint32 value) |

| MRCC_GLB_ACC1 - PORT0. | |

| static constexpr uint32 | GLB_ACC1_PORT1 (uint32 value) |

| MRCC_GLB_ACC1 - PORT1. | |

| static constexpr uint32 | GLB_ACC1_PORT2 (uint32 value) |

| MRCC_GLB_ACC1 - PORT2. | |

| static constexpr uint32 | GLB_ACC1_PORT3 (uint32 value) |

| MRCC_GLB_ACC1 - PORT3. | |

| static constexpr uint32 | GLB_ACC1_PORT4 (uint32 value) |

| MRCC_GLB_ACC1 - PORT4. | |

| static constexpr uint32 | GLB_ACC1_FLEXCAN0 (uint32 value) |

| MRCC_GLB_ACC1 - FLEXCAN0. | |

| static constexpr uint32 | GLB_ACC1_LPI2C2 (uint32 value) |

| MRCC_GLB_ACC1 - LPI2C2. | |

| static constexpr uint32 | GLB_ACC1_LPI2C3 (uint32 value) |

| MRCC_GLB_ACC1 - LPI2C3. | |

| static constexpr uint32 | GLB_ACC1_RAMA (uint32 value) |

| MRCC_GLB_ACC1 - RAMA. | |

| static constexpr uint32 | GLB_ACC1_RAMB (uint32 value) |

| MRCC_GLB_ACC1 - RAMB. | |

| static constexpr uint32 | GLB_ACC1_GPIO0 (uint32 value) |

| MRCC_GLB_ACC1 - GPIO0. | |

| static constexpr uint32 | GLB_ACC1_GPIO1 (uint32 value) |

| MRCC_GLB_ACC1 - GPIO1. | |

| static constexpr uint32 | GLB_ACC1_GPIO2 (uint32 value) |

| MRCC_GLB_ACC1 - GPIO2. | |

| static constexpr uint32 | GLB_ACC1_GPIO3 (uint32 value) |

| MRCC_GLB_ACC1 - GPIO3. | |

| static constexpr uint32 | GLB_ACC1_GPIO4 (uint32 value) |

| MRCC_GLB_ACC1 - GPIO4. | |

| static constexpr uint32 | GLB_ACC1_ROMC (uint32 value) |

| MRCC_GLB_ACC1 - ROMC. | |

| static constexpr uint32 | I3C0_FCLK_CLKSEL_MUX (uint32 value) |

| MRCC_I3C0_FCLK_CLKSEL - MUX. | |

| static constexpr uint32 | I3C0_FCLK_CLKDIV_DIV (uint32 value) |

| MRCC_I3C0_FCLK_CLKDIV - DIV. | |

| static constexpr uint32 | I3C0_FCLK_CLKDIV_RESET (uint32 value) |

| MRCC_I3C0_FCLK_CLKDIV - RESET. | |

| static constexpr uint32 | I3C0_FCLK_CLKDIV_HALT (uint32 value) |

| MRCC_I3C0_FCLK_CLKDIV - HALT. | |

| static constexpr uint32 | I3C0_FCLK_CLKDIV_UNSTAB (uint32 value) |

| MRCC_I3C0_FCLK_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CTIMER0_CLKSEL_MUX (uint32 value) |

| MRCC_CTIMER0_CLKSEL - MUX. | |

| static constexpr uint32 | CTIMER0_CLKDIV_DIV (uint32 value) |

| MRCC_CTIMER0_CLKDIV - DIV. | |

| static constexpr uint32 | CTIMER0_CLKDIV_RESET (uint32 value) |

| MRCC_CTIMER0_CLKDIV - RESET. | |

| static constexpr uint32 | CTIMER0_CLKDIV_HALT (uint32 value) |

| MRCC_CTIMER0_CLKDIV - HALT. | |

| static constexpr uint32 | CTIMER0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CTIMER0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CTIMER1_CLKSEL_MUX (uint32 value) |

| MRCC_CTIMER1_CLKSEL - MUX. | |

| static constexpr uint32 | CTIMER1_CLKDIV_DIV (uint32 value) |

| MRCC_CTIMER1_CLKDIV - DIV. | |

| static constexpr uint32 | CTIMER1_CLKDIV_RESET (uint32 value) |

| MRCC_CTIMER1_CLKDIV - RESET. | |

| static constexpr uint32 | CTIMER1_CLKDIV_HALT (uint32 value) |

| MRCC_CTIMER1_CLKDIV - HALT. | |

| static constexpr uint32 | CTIMER1_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CTIMER1_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CTIMER2_CLKSEL_MUX (uint32 value) |

| MRCC_CTIMER2_CLKSEL - MUX. | |

| static constexpr uint32 | CTIMER2_CLKDIV_DIV (uint32 value) |

| MRCC_CTIMER2_CLKDIV - DIV. | |

| static constexpr uint32 | CTIMER2_CLKDIV_RESET (uint32 value) |

| MRCC_CTIMER2_CLKDIV - RESET. | |

| static constexpr uint32 | CTIMER2_CLKDIV_HALT (uint32 value) |

| MRCC_CTIMER2_CLKDIV - HALT. | |

| static constexpr uint32 | CTIMER2_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CTIMER2_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CTIMER3_CLKSEL_MUX (uint32 value) |

| MRCC_CTIMER3_CLKSEL - MUX. | |

| static constexpr uint32 | CTIMER3_CLKDIV_DIV (uint32 value) |

| MRCC_CTIMER3_CLKDIV - DIV. | |

| static constexpr uint32 | CTIMER3_CLKDIV_RESET (uint32 value) |

| MRCC_CTIMER3_CLKDIV - RESET. | |

| static constexpr uint32 | CTIMER3_CLKDIV_HALT (uint32 value) |

| MRCC_CTIMER3_CLKDIV - HALT. | |

| static constexpr uint32 | CTIMER3_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CTIMER3_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CTIMER4_CLKSEL_MUX (uint32 value) |

| MRCC_CTIMER4_CLKSEL - MUX. | |

| static constexpr uint32 | CTIMER4_CLKDIV_DIV (uint32 value) |

| MRCC_CTIMER4_CLKDIV - DIV. | |

| static constexpr uint32 | CTIMER4_CLKDIV_RESET (uint32 value) |

| MRCC_CTIMER4_CLKDIV - RESET. | |

| static constexpr uint32 | CTIMER4_CLKDIV_HALT (uint32 value) |

| MRCC_CTIMER4_CLKDIV - HALT. | |

| static constexpr uint32 | CTIMER4_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CTIMER4_CLKDIV - UNSTAB. | |

| static constexpr uint32 | WWDT0_CLKDIV_DIV (uint32 value) |

| MRCC_WWDT0_CLKDIV - DIV. | |

| static constexpr uint32 | WWDT0_CLKDIV_RESET (uint32 value) |

| MRCC_WWDT0_CLKDIV - RESET. | |

| static constexpr uint32 | WWDT0_CLKDIV_HALT (uint32 value) |

| MRCC_WWDT0_CLKDIV - HALT. | |

| static constexpr uint32 | WWDT0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_WWDT0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | FLEXIO0_CLKSEL_MUX (uint32 value) |

| MRCC_FLEXIO0_CLKSEL - MUX. | |

| static constexpr uint32 | FLEXIO0_CLKDIV_DIV (uint32 value) |

| MRCC_FLEXIO0_CLKDIV - DIV. | |

| static constexpr uint32 | FLEXIO0_CLKDIV_RESET (uint32 value) |

| MRCC_FLEXIO0_CLKDIV - RESET. | |

| static constexpr uint32 | FLEXIO0_CLKDIV_HALT (uint32 value) |

| MRCC_FLEXIO0_CLKDIV - HALT. | |

| static constexpr uint32 | FLEXIO0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_FLEXIO0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPI2C0_CLKSEL_MUX (uint32 value) |

| MRCC_LPI2C0_CLKSEL - MUX. | |

| static constexpr uint32 | LPI2C0_CLKDIV_DIV (uint32 value) |

| MRCC_LPI2C0_CLKDIV - DIV. | |

| static constexpr uint32 | LPI2C0_CLKDIV_RESET (uint32 value) |

| MRCC_LPI2C0_CLKDIV - RESET. | |

| static constexpr uint32 | LPI2C0_CLKDIV_HALT (uint32 value) |

| MRCC_LPI2C0_CLKDIV - HALT. | |

| static constexpr uint32 | LPI2C0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPI2C0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPI2C1_CLKSEL_MUX (uint32 value) |

| MRCC_LPI2C1_CLKSEL - MUX. | |

| static constexpr uint32 | LPI2C1_CLKDIV_DIV (uint32 value) |

| MRCC_LPI2C1_CLKDIV - DIV. | |

| static constexpr uint32 | LPI2C1_CLKDIV_RESET (uint32 value) |

| MRCC_LPI2C1_CLKDIV - RESET. | |

| static constexpr uint32 | LPI2C1_CLKDIV_HALT (uint32 value) |

| MRCC_LPI2C1_CLKDIV - HALT. | |

| static constexpr uint32 | LPI2C1_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPI2C1_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPSPI0_CLKSEL_MUX (uint32 value) |

| MRCC_LPSPI0_CLKSEL - MUX. | |

| static constexpr uint32 | LPSPI0_CLKDIV_DIV (uint32 value) |

| MRCC_LPSPI0_CLKDIV - DIV. | |

| static constexpr uint32 | LPSPI0_CLKDIV_RESET (uint32 value) |

| MRCC_LPSPI0_CLKDIV - RESET. | |

| static constexpr uint32 | LPSPI0_CLKDIV_HALT (uint32 value) |

| MRCC_LPSPI0_CLKDIV - HALT. | |

| static constexpr uint32 | LPSPI0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPSPI0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPSPI1_CLKSEL_MUX (uint32 value) |

| MRCC_LPSPI1_CLKSEL - MUX. | |

| static constexpr uint32 | LPSPI1_CLKDIV_DIV (uint32 value) |

| MRCC_LPSPI1_CLKDIV - DIV. | |

| static constexpr uint32 | LPSPI1_CLKDIV_RESET (uint32 value) |

| MRCC_LPSPI1_CLKDIV - RESET. | |

| static constexpr uint32 | LPSPI1_CLKDIV_HALT (uint32 value) |

| MRCC_LPSPI1_CLKDIV - HALT. | |

| static constexpr uint32 | LPSPI1_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPSPI1_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPUART0_CLKSEL_MUX (uint32 value) |

| MRCC_LPUART0_CLKSEL - MUX. | |

| static constexpr uint32 | LPUART0_CLKDIV_DIV (uint32 value) |

| MRCC_LPUART0_CLKDIV - DIV. | |

| static constexpr uint32 | LPUART0_CLKDIV_RESET (uint32 value) |

| MRCC_LPUART0_CLKDIV - RESET. | |

| static constexpr uint32 | LPUART0_CLKDIV_HALT (uint32 value) |

| MRCC_LPUART0_CLKDIV - HALT. | |

| static constexpr uint32 | LPUART0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPUART0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPUART1_CLKSEL_MUX (uint32 value) |

| MRCC_LPUART1_CLKSEL - MUX. | |

| static constexpr uint32 | LPUART1_CLKDIV_DIV (uint32 value) |

| MRCC_LPUART1_CLKDIV - DIV. | |

| static constexpr uint32 | LPUART1_CLKDIV_RESET (uint32 value) |

| MRCC_LPUART1_CLKDIV - RESET. | |

| static constexpr uint32 | LPUART1_CLKDIV_HALT (uint32 value) |

| MRCC_LPUART1_CLKDIV - HALT. | |

| static constexpr uint32 | LPUART1_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPUART1_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPUART2_CLKSEL_MUX (uint32 value) |

| MRCC_LPUART2_CLKSEL - MUX. | |

| static constexpr uint32 | LPUART2_CLKDIV_DIV (uint32 value) |

| MRCC_LPUART2_CLKDIV - DIV. | |

| static constexpr uint32 | LPUART2_CLKDIV_RESET (uint32 value) |

| MRCC_LPUART2_CLKDIV - RESET. | |

| static constexpr uint32 | LPUART2_CLKDIV_HALT (uint32 value) |

| MRCC_LPUART2_CLKDIV - HALT. | |

| static constexpr uint32 | LPUART2_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPUART2_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPUART3_CLKSEL_MUX (uint32 value) |

| MRCC_LPUART3_CLKSEL - MUX. | |

| static constexpr uint32 | LPUART3_CLKDIV_DIV (uint32 value) |

| MRCC_LPUART3_CLKDIV - DIV. | |

| static constexpr uint32 | LPUART3_CLKDIV_RESET (uint32 value) |

| MRCC_LPUART3_CLKDIV - RESET. | |

| static constexpr uint32 | LPUART3_CLKDIV_HALT (uint32 value) |

| MRCC_LPUART3_CLKDIV - HALT. | |

| static constexpr uint32 | LPUART3_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPUART3_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPUART4_CLKSEL_MUX (uint32 value) |

| MRCC_LPUART4_CLKSEL - MUX. | |

| static constexpr uint32 | LPUART4_CLKDIV_DIV (uint32 value) |

| MRCC_LPUART4_CLKDIV - DIV. | |

| static constexpr uint32 | LPUART4_CLKDIV_RESET (uint32 value) |

| MRCC_LPUART4_CLKDIV - RESET. | |

| static constexpr uint32 | LPUART4_CLKDIV_HALT (uint32 value) |

| MRCC_LPUART4_CLKDIV - HALT. | |

| static constexpr uint32 | LPUART4_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPUART4_CLKDIV - UNSTAB. | |

| static constexpr uint32 | USB0_CLKSEL_MUX (uint32 value) |

| MRCC_USB0_CLKSEL - MUX. | |

| static constexpr uint32 | LPTMR0_CLKSEL_MUX (uint32 value) |

| MRCC_LPTMR0_CLKSEL - MUX. | |

| static constexpr uint32 | LPTMR0_CLKDIV_DIV (uint32 value) |

| MRCC_LPTMR0_CLKDIV - DIV. | |

| static constexpr uint32 | LPTMR0_CLKDIV_RESET (uint32 value) |

| MRCC_LPTMR0_CLKDIV - RESET. | |

| static constexpr uint32 | LPTMR0_CLKDIV_HALT (uint32 value) |

| MRCC_LPTMR0_CLKDIV - HALT. | |

| static constexpr uint32 | LPTMR0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPTMR0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | OSTIMER0_CLKSEL_MUX (uint32 value) |

| MRCC_OSTIMER0_CLKSEL - MUX. | |

| static constexpr uint32 | ADC0_CLKSEL_MUX (uint32 value) |

| MRCC_ADC0_CLKSEL - MUX. | |

| static constexpr uint32 | ADC0_CLKDIV_DIV (uint32 value) |

| MRCC_ADC0_CLKDIV - DIV. | |

| static constexpr uint32 | ADC0_CLKDIV_RESET (uint32 value) |

| MRCC_ADC0_CLKDIV - RESET. | |

| static constexpr uint32 | ADC0_CLKDIV_HALT (uint32 value) |

| MRCC_ADC0_CLKDIV - HALT. | |

| static constexpr uint32 | ADC0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_ADC0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | ADC1_CLKSEL_MUX (uint32 value) |

| MRCC_ADC1_CLKSEL - MUX. | |

| static constexpr uint32 | ADC1_CLKDIV_DIV (uint32 value) |

| MRCC_ADC1_CLKDIV - DIV. | |

| static constexpr uint32 | ADC1_CLKDIV_RESET (uint32 value) |

| MRCC_ADC1_CLKDIV - RESET. | |

| static constexpr uint32 | ADC1_CLKDIV_HALT (uint32 value) |

| MRCC_ADC1_CLKDIV - HALT. | |

| static constexpr uint32 | ADC1_CLKDIV_UNSTAB (uint32 value) |

| MRCC_ADC1_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CMP0_FUNC_CLKDIV_DIV (uint32 value) |

| MRCC_CMP0_FUNC_CLKDIV - DIV. | |

| static constexpr uint32 | CMP0_FUNC_CLKDIV_RESET (uint32 value) |

| MRCC_CMP0_FUNC_CLKDIV - RESET. | |

| static constexpr uint32 | CMP0_FUNC_CLKDIV_HALT (uint32 value) |

| MRCC_CMP0_FUNC_CLKDIV - HALT. | |

| static constexpr uint32 | CMP0_FUNC_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CMP0_FUNC_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CMP0_RR_CLKSEL_MUX (uint32 value) |

| MRCC_CMP0_RR_CLKSEL - MUX. | |

| static constexpr uint32 | CMP0_RR_CLKDIV_DIV (uint32 value) |

| MRCC_CMP0_RR_CLKDIV - DIV. | |

| static constexpr uint32 | CMP0_RR_CLKDIV_RESET (uint32 value) |

| MRCC_CMP0_RR_CLKDIV - RESET. | |

| static constexpr uint32 | CMP0_RR_CLKDIV_HALT (uint32 value) |

| MRCC_CMP0_RR_CLKDIV - HALT. | |

| static constexpr uint32 | CMP0_RR_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CMP0_RR_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CMP1_FUNC_CLKDIV_DIV (uint32 value) |

| MRCC_CMP1_FUNC_CLKDIV - DIV. | |

| static constexpr uint32 | CMP1_FUNC_CLKDIV_RESET (uint32 value) |

| MRCC_CMP1_FUNC_CLKDIV - RESET. | |

| static constexpr uint32 | CMP1_FUNC_CLKDIV_HALT (uint32 value) |

| MRCC_CMP1_FUNC_CLKDIV - HALT. | |

| static constexpr uint32 | CMP1_FUNC_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CMP1_FUNC_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CMP1_RR_CLKSEL_MUX (uint32 value) |

| MRCC_CMP1_RR_CLKSEL - MUX. | |

| static constexpr uint32 | CMP1_RR_CLKDIV_DIV (uint32 value) |

| MRCC_CMP1_RR_CLKDIV - CDIV. | |

| static constexpr uint32 | CMP1_RR_CLKDIV_RESET (uint32 value) |

| MRCC_CMP1_RR_CLKDIV - CRESET. | |

| static constexpr uint32 | CMP1_RR_CLKDIV_HALT (uint32 value) |

| MRCC_CMP1_RR_CLKDIV - CHALT. | |

| static constexpr uint32 | CMP1_RR_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CMP1_RR_CLKDIV - CUNSTAB. | |

| static constexpr uint32 | DAC0_CLKSEL_MUX (uint32 value) |

| MRCC_DAC0_CLKSEL - MUX. | |

| static constexpr uint32 | DAC0_CLKDIV_DIV (uint32 value) |

| MRCC_DAC0_CLKDIV - DIV. | |

| static constexpr uint32 | DAC0_CLKDIV_RESET (uint32 value) |

| MRCC_DAC0_CLKDIV - RESET. | |

| static constexpr uint32 | DAC0_CLKDIV_HALT (uint32 value) |

| MRCC_DAC0_CLKDIV - HALT. | |

| static constexpr uint32 | DAC0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_DAC0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | FLEXCAN0_CLKSEL_MUX (uint32 value) |

| MRCC_FLEXCAN0_CLKSEL - MUX. | |

| static constexpr uint32 | FLEXCAN0_CLKDIV_DIV (uint32 value) |

| MRCC_FLEXCAN0_CLKDIV - DIV. | |

| static constexpr uint32 | FLEXCAN0_CLKDIV_RESET (uint32 value) |

| MRCC_FLEXCAN0_CLKDIV - RESET. | |

| static constexpr uint32 | FLEXCAN0_CLKDIV_HALT (uint32 value) |

| MRCC_FLEXCAN0_CLKDIV - HALT. | |

| static constexpr uint32 | FLEXCAN0_CLKDIV_UNSTAB (uint32 value) |

| MRCC_FLEXCAN0_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPI2C2_CLKSEL_MUX (uint32 value) |

| MRCC_LPI2C2_CLKSEL - MUX. | |

| static constexpr uint32 | LPI2C2_CLKDIV_DIV (uint32 value) |

| MRCC_LPI2C2_CLKDIV - DIV. | |

| static constexpr uint32 | LPI2C2_CLKDIV_RESET (uint32 value) |

| MRCC_LPI2C2_CLKDIV - RESET. | |

| static constexpr uint32 | LPI2C2_CLKDIV_HALT (uint32 value) |

| MRCC_LPI2C2_CLKDIV - HALT. | |

| static constexpr uint32 | LPI2C2_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPI2C2_CLKDIV - UNSTAB. | |

| static constexpr uint32 | LPI2C3_CLKSEL_MUX (uint32 value) |

| MRCC_LPI2C3_CLKSEL - MUX. | |

| static constexpr uint32 | LPI2C3_CLKDIV_DIV (uint32 value) |

| MRCC_LPI2C3_CLKDIV - DIV. | |

| static constexpr uint32 | LPI2C3_CLKDIV_RESET (uint32 value) |

| MRCC_LPI2C3_CLKDIV - RESET. | |

| static constexpr uint32 | LPI2C3_CLKDIV_HALT (uint32 value) |

| MRCC_LPI2C3_CLKDIV - HALT. | |

| static constexpr uint32 | LPI2C3_CLKDIV_UNSTAB (uint32 value) |

| MRCC_LPI2C3_CLKDIV - UNSTAB. | |

| static constexpr uint32 | DBG_TRACE_CLKSEL_MUX (uint32 value) |

| MRCC_DBG_TRACE_CLKSEL - MUX. | |

| static constexpr uint32 | DBG_TRACE_CLKDIV_DIV (uint32 value) |

| MRCC_DBG_TRACE_CLKDIV - DIV. | |

| static constexpr uint32 | DBG_TRACE_CLKDIV_RESET (uint32 value) |

| MRCC_DBG_TRACE_CLKDIV - RESET. | |

| static constexpr uint32 | DBG_TRACE_CLKDIV_HALT (uint32 value) |

| MRCC_DBG_TRACE_CLKDIV - HALT. | |

| static constexpr uint32 | DBG_TRACE_CLKDIV_UNSTAB (uint32 value) |

| MRCC_DBG_TRACE_CLKDIV - UNSTAB. | |

| static constexpr uint32 | CLKOUT_CLKSEL_MUX (uint32 value) |

| MRCC_CLKOUT_CLKSEL - MUX. | |

| static constexpr uint32 | CLKOUT_CLKDIV_DIV (uint32 value) |

| MRCC_CLKOUT_CLKDIV - DIV. | |

| static constexpr uint32 | CLKOUT_CLKDIV_RESET (uint32 value) |

| MRCC_CLKOUT_CLKDIV - RESET. | |

| static constexpr uint32 | CLKOUT_CLKDIV_HALT (uint32 value) |

| MRCC_CLKOUT_CLKDIV - HALT. | |

| static constexpr uint32 | CLKOUT_CLKDIV_UNSTAB (uint32 value) |

| MRCC_CLKOUT_CLKDIV - UNSTAB. | |

| static constexpr uint32 | SYSTICK_CLKSEL_MUX (uint32 value) |

| MRCC_SYSTICK_CLKSEL - MUX. | |

| static constexpr uint32 | SYSTICK_CLKDIV_DIV (uint32 value) |

| MRCC_SYSTICK_CLKDIV - DIV. | |

| static constexpr uint32 | SYSTICK_CLKDIV_RESET (uint32 value) |

| MRCC_SYSTICK_CLKDIV - RESET. | |

| static constexpr uint32 | SYSTICK_CLKDIV_HALT (uint32 value) |

| MRCC_SYSTICK_CLKDIV - HALT. | |

| static constexpr uint32 | SYSTICK_CLKDIV_UNSTAB (uint32 value) |

| MRCC_SYSTICK_CLKDIV - UNSTAB. | |

| static constexpr uint32 | FRO_HF_DIV_CLKDIV_DIV (uint32 value) |

| MRCC_FRO_HF_DIV_CLKDIV - DIV. | |

| static constexpr uint32 | FRO_HF_DIV_CLKDIV_UNSTAB (uint32 value) |

| MRCC_FRO_HF_DIV_CLKDIV - UNSTAB. | |

函式成員說明文件

◆ ADC0_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_ADC0_CLKDIV - DIV.

ADC0 clock divider control - Functional Clock Divider

◆ ADC0_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_ADC0_CLKDIV - HALT.

ADC0 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ ADC0_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_ADC0_CLKDIV - RESET.

ADC0 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ ADC0_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_ADC0_CLKDIV - UNSTAB.

ADC0 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ ADC0_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_ADC0_CLKSEL - MUX.

ADC0 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ ADC1_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_ADC1_CLKDIV - DIV.

ADC1 clock divider control - Functional Clock Divider

◆ ADC1_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_ADC1_CLKDIV - HALT.

ADC1 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ ADC1_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_ADC1_CLKDIV - RESET.

ADC1 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ ADC1_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_ADC1_CLKDIV - UNSTAB.

ADC1 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ ADC1_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_ADC1_CLKSEL - MUX.

ADC1 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ CLKOUT_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CLKOUT_CLKDIV - DIV.

CLKOUT clock divider control - Functional Clock Divider

◆ CLKOUT_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CLKOUT_CLKDIV - HALT.

CLKOUT clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CLKOUT_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CLKOUT_CLKDIV - RESET.

CLKOUT clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CLKOUT_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CLKOUT_CLKDIV - UNSTAB.

CLKOUT clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CLKOUT_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CLKOUT_CLKSEL - MUX.

CLKOUT clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b110]SLOW_CLK

- [0b011]CLK_16K

- [0b010]CLK_IN

- [0b001]FRO_HF_DIV

- [0b000]FRO_12M

◆ CMP0_FUNC_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CMP0_FUNC_CLKDIV - DIV.

CMP0_FUNC clock divider control - Functional Clock Divider

◆ CMP0_FUNC_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CMP0_FUNC_CLKDIV - HALT.

CMP0_FUNC clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CMP0_FUNC_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CMP0_FUNC_CLKDIV - RESET.

CMP0_FUNC clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CMP0_FUNC_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CMP0_FUNC_CLKDIV - UNSTAB.

CMP0_FUNC clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CMP0_RR_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CMP0_RR_CLKDIV - DIV.

CMP0_RR clock divider control - Functional Clock Divider

◆ CMP0_RR_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CMP0_RR_CLKDIV - HALT.

CMP0_RR clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CMP0_RR_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CMP0_RR_CLKDIV - RESET.

CMP0_RR clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CMP0_RR_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CMP0_RR_CLKDIV - UNSTAB.

CMP0_RR clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CMP0_RR_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CMP0_RR_CLKSEL - MUX.

CMP0_RR clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b011]CLK_IN

- [0b010]FRO_HF_DIV

- [0b000]FRO_12M

◆ CMP1_FUNC_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CMP1_FUNC_CLKDIV - DIV.

CMP1_FUNC clock divider control - Functional Clock Divider

◆ CMP1_FUNC_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CMP1_FUNC_CLKDIV - HALT.

CMP1_FUNC clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CMP1_FUNC_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CMP1_FUNC_CLKDIV - RESET.

CMP1_FUNC clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CMP1_FUNC_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CMP1_FUNC_CLKDIV - UNSTAB.

CMP1_FUNC clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CMP1_RR_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CMP1_RR_CLKDIV - CDIV.

CMP1_RR clock divider control - Functional Clock Divider

◆ CMP1_RR_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CMP1_RR_CLKDIV - CHALT.

CMP1_RR clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CMP1_RR_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CMP1_RR_CLKDIV - CRESET.

CMP1_RR clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CMP1_RR_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CMP1_RR_CLKDIV - CUNSTAB.

CMP1_RR clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CMP1_RR_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CMP1_RR_CLKSEL - MUX.

CMP1_RR clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b011]CLK_IN

- [0b010]FRO_HF_DIV

- [0b000]FRO_12M

◆ CTIMER0_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CTIMER0_CLKDIV - DIV.

CTIMER0 clock divider control - Functional Clock Divider

◆ CTIMER0_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CTIMER0_CLKDIV - HALT.

CTIMER0 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CTIMER0_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CTIMER0_CLKDIV - RESET.

CTIMER0 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CTIMER0_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CTIMER0_CLKDIV - UNSTAB.

CTIMER0 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CTIMER0_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CTIMER0_CLKSEL - MUX.

CTIMER0 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b100]CLK_16K

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ CTIMER1_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CTIMER1_CLKDIV - DIV.

CTIMER1 clock divider control - Functional Clock Divider

◆ CTIMER1_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CTIMER1_CLKDIV - HALT.

CTIMER1 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CTIMER1_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CTIMER1_CLKDIV - RESET.

CTIMER1 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CTIMER1_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CTIMER1_CLKDIV - UNSTAB.

CTIMER1 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CTIMER1_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CTIMER1_CLKSEL - MUX.

CTIMER1 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b100]CLK_16K

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ CTIMER2_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CTIMER2_CLKDIV - DIV.

CTIMER2 clock divider control - Functional Clock Divider

◆ CTIMER2_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CTIMER2_CLKDIV - HALT.

CTIMER2 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CTIMER2_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CTIMER2_CLKDIV - RESET.

CTIMER2 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CTIMER2_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CTIMER2_CLKDIV - UNSTAB.

CTIMER2 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CTIMER2_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CTIMER2_CLKSEL - MUX.

CTIMER2 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b100]CLK_16K

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ CTIMER3_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CTIMER3_CLKDIV - DIV.

CTIMER3 clock divider control - Functional Clock Divider

◆ CTIMER3_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CTIMER3_CLKDIV - HALT.

CTIMER3 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CTIMER3_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CTIMER3_CLKDIV - RESET.

CTIMER3 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CTIMER3_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CTIMER3_CLKDIV - UNSTAB.

CTIMER3 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CTIMER3_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CTIMER3_CLKSEL - MUX.

CTIMER3 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b100]CLK_16K

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ CTIMER4_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_CTIMER4_CLKDIV - DIV.

CTIMER4 clock divider control - Functional Clock Divider

◆ CTIMER4_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_CTIMER4_CLKDIV - HALT.

CTIMER4 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ CTIMER4_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_CTIMER4_CLKDIV - RESET.

CTIMER4 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ CTIMER4_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_CTIMER4_CLKDIV - UNSTAB.

CTIMER4 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ CTIMER4_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_CTIMER4_CLKSEL - MUX.

CTIMER4 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b100]CLK_16K

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ DAC0_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_DAC0_CLKDIV - DIV.

DAC0 clock divider control - Functional Clock Divider

◆ DAC0_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_DAC0_CLKDIV - HALT.

DAC0 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ DAC0_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_DAC0_CLKDIV - RESET.

DAC0 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ DAC0_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_DAC0_CLKDIV - UNSTAB.

DAC0 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ DAC0_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_DAC0_CLKSEL - MUX.

DAC0 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b011]CLK_IN

- [0b010]FRO_HF_DIV

- [0b000]FRO_12M

◆ DBG_TRACE_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_DBG_TRACE_CLKDIV - DIV.

DBG_TRACE clock divider control - Functional Clock Divider

◆ DBG_TRACE_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_DBG_TRACE_CLKDIV - HALT.

DBG_TRACE clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ DBG_TRACE_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_DBG_TRACE_CLKDIV - RESET.

DBG_TRACE clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ DBG_TRACE_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_DBG_TRACE_CLKDIV - UNSTAB.

DBG_TRACE clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ DBG_TRACE_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_DBG_TRACE_CLKSEL - MUX.

DBG_TRACE clock selection control - Functional Clock Mux Select

- [0b11]Reserved1(NO Clock)

- [0b10]CLK_16K

- [0b01]CLK_1M

- [0b00]CPU_CLK

◆ FLEXCAN0_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_FLEXCAN0_CLKDIV - DIV.

FLEXCAN0 clock divider control - Functional Clock Divider

◆ FLEXCAN0_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_FLEXCAN0_CLKDIV - HALT.

FLEXCAN0 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ FLEXCAN0_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_FLEXCAN0_CLKDIV - RESET.

FLEXCAN0 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ FLEXCAN0_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_FLEXCAN0_CLKDIV - UNSTAB.

FLEXCAN0 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ FLEXCAN0_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_FLEXCAN0_CLKSEL - MUX.

FLEXCAN0 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b011]CLK_IN

- [0b010]FRO_HF_DIV

◆ FLEXIO0_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_FLEXIO0_CLKDIV - DIV.

FLEXIO0 clock divider control - Functional Clock Divider

◆ FLEXIO0_CLKDIV_HALT()

|

inlinestaticconstexpr |

MRCC_FLEXIO0_CLKDIV - HALT.

FLEXIO0 clock divider control - Halt divider counter

- [0b0]Divider clock is running

- [0b1]Divider clock is stopped

◆ FLEXIO0_CLKDIV_RESET()

|

inlinestaticconstexpr |

MRCC_FLEXIO0_CLKDIV - RESET.

FLEXIO0 clock divider control - Reset divider counter

- [0b0]Divider isn't reset

- [0b1]Divider is reset

◆ FLEXIO0_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_FLEXIO0_CLKDIV - UNSTAB.

FLEXIO0 clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ FLEXIO0_CLKSEL_MUX()

|

inlinestaticconstexpr |

MRCC_FLEXIO0_CLKSEL - MUX.

FLEXIO0 clock selection control - Functional Clock Mux Select

- [0b111]Reserved(NO Clock)

- [0b101]CLK_1M

- [0b011]CLK_IN

- [0b001]FRO_HF_GATED

- [0b000]FRO_12M

◆ FRO_HF_DIV_CLKDIV_DIV()

|

inlinestaticconstexpr |

MRCC_FRO_HF_DIV_CLKDIV - DIV.

FRO_HF_DIV clock divider control - Functional Clock Divider

◆ FRO_HF_DIV_CLKDIV_UNSTAB()

|

inlinestaticconstexpr |

MRCC_FRO_HF_DIV_CLKDIV - UNSTAB.

FRO_HF_DIV clock divider control - Divider status flag

- [0b0]Divider clock is stable

- [0b1]Clock frequency isn't stable

◆ GLB_ACC0_AOI0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - AOI0.

Control Automatic Clock Gating 0 - AOI0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_AOI1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - AOI1.

Control Automatic Clock Gating 0 - AOI1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_CRC0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - CRC0.

Control Automatic Clock Gating 0 - CRC0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_CTIMER0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - CTIMER0.

Control Automatic Clock Gating 0 - CTIMER0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_CTIMER1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - CTIMER1.

Control Automatic Clock Gating 0 - CTIMER1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_CTIMER2()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - CTIMER2.

Control Automatic Clock Gating 0 - CTIMER2

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_CTIMER3()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - CTIMER3.

Control Automatic Clock Gating 0 - CTIMER3

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_CTIMER4()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - CTIMER4.

Control Automatic Clock Gating 0 - CTIMER4

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_DMA()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - DMA.

Control Automatic Clock Gating 0 - DMA

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_EIM0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - EIM0.

Control Automatic Clock Gating 0 - EIM0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_ERM0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - ERM0.

Control Automatic Clock Gating 0 - ERM0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_FLEXIO0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - FLEXIO0.

Control Automatic Clock Gating 0 - FLEXIO0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_FLEXPWM0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - FLEXPWM0.

Control Automatic Clock Gating 0 - FLEXPWM0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_FLEXPWM1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - FLEXPWM1.

Control Automatic Clock Gating 0 - FLEXPWM1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_FMC()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - FMC.

Control Automatic Clock Gating 0 - FMC

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_FREQME()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - FREQME.

Control Automatic Clock Gating 0 - FREQME

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_I3C0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - I3C0.

Control Automatic Clock Gating 0 - I3C0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_INPUTMUX0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - INPUTMUX0.

Control Automatic Clock Gating 0 - INPUTMUX0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPI2C0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPI2C0.

Control Automatic Clock Gating 0 - LPI2C0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPI2C1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPI2C1.

Control Automatic Clock Gating 0 - LPI2C1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPSPI0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPSPI0.

Control Automatic Clock Gating 0 - LPSPI0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPSPI1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPSPI1.

Control Automatic Clock Gating 0 - LPSPI1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPUART0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPUART0.

Control Automatic Clock Gating 0 - LPUART0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPUART1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPUART1.

Control Automatic Clock Gating 0 - LPUART1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPUART2()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPUART2.

Control Automatic Clock Gating 0 - LPUART2

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPUART3()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPUART3.

Control Automatic Clock Gating 0 - LPUART3

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_LPUART4()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - LPUART4.

Control Automatic Clock Gating 0 - LPUART4

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_QDC0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - QDC0.

Control Automatic Clock Gating 0 - QDC0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_QDC1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - QDC1.

Control Automatic Clock Gating 0 - QDC1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_USB0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - USB0.

Control Automatic Clock Gating 0 - USB0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_UTICK0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - UTICK0.

Control Automatic Clock Gating 0 - UTICK0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC0_WWDT0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC0 - WWDT0.

Control Automatic Clock Gating 0 - WWDT0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_ADC0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - ADC0.

Control Automatic Clock Gating 1 - ADC0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_ADC1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - ADC1.

Control Automatic Clock Gating 1 - ADC1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_CMP0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - CMP0.

Control Automatic Clock Gating 1 - CMP0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_CMP1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - CMP1.

Control Automatic Clock Gating 1 - CMP1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_DAC0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - DAC0.

Control Automatic Clock Gating 1 - DAC0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_FLEXCAN0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - FLEXCAN0.

Control Automatic Clock Gating 1 - FLEXCAN0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_GPIO0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - GPIO0.

Control Automatic Clock Gating 1 - GPIO0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_GPIO1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - GPIO1.

Control Automatic Clock Gating 1 - GPIO1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_GPIO2()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - GPIO2.

Control Automatic Clock Gating 1 - GPIO2

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_GPIO3()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - GPIO3.

Control Automatic Clock Gating 1 - GPIO3

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_GPIO4()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - GPIO4.

Control Automatic Clock Gating 1 - GPIO4

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_LPI2C2()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - LPI2C2.

Control Automatic Clock Gating 1 - LPI2C2

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_LPI2C3()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - LPI2C3.

Control Automatic Clock Gating 1 - LPI2C3

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_OPAMP0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - OPAMP0.

Control Automatic Clock Gating 1 - OPAMP0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_OSTIMER0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - OSTIMER0.

Control Automatic Clock Gating 1 - OSTIMER0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_PORT0()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - PORT0.

Control Automatic Clock Gating 1 - PORT0

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_PORT1()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - PORT1.

Control Automatic Clock Gating 1 - PORT1

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_PORT2()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - PORT2.

Control Automatic Clock Gating 1 - PORT2

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_PORT3()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - PORT3.

Control Automatic Clock Gating 1 - PORT3

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_PORT4()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - PORT4.

Control Automatic Clock Gating 1 - PORT4

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_RAMA()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - RAMA.

Control Automatic Clock Gating 1 - RAMA

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_RAMB()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - RAMB.

Control Automatic Clock Gating 1 - RAMB

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_ACC1_ROMC()

|

inlinestaticconstexpr |

MRCC_GLB_ACC1 - ROMC.

Control Automatic Clock Gating 1 - ROMC

- [0b0]Automatic clock gating is disabled

- [0b1]Automatic clock gating is enabled

◆ GLB_CC0_AOI0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - AOI0.

AHB Clock Control 0 - AOI0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_AOI1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - AOI1.

AHB Clock Control 0 - AOI1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_CLR_DATA()

|

inlinestaticconstexpr |

MRCC_GLB_CC0_CLR - DATA.

AHB Clock Control Clear 0 - Data array value, refer to corresponding position in MRCC_GLB_CCn.

◆ GLB_CC0_CRC0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - CRC0.

AHB Clock Control 0 - CRC0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_CTIMER0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - CTIMER0.

AHB Clock Control 0 - CTIMER0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_CTIMER1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - CTIMER1.

AHB Clock Control 0 - CTIMER1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_CTIMER2()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - CTIMER2.

AHB Clock Control 0 - CTIMER2

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_CTIMER3()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - CTIMER3.

AHB Clock Control 0 - CTIMER3

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_CTIMER4()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - CTIMER4.

AHB Clock Control 0 - CTIMER4

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_DMA()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - DMA.

AHB Clock Control 0 - DMA

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_EIM0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - EIM0.

AHB Clock Control 0 - EIM0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_ERM0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - ERM0.

AHB Clock Control 0 - ERM0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_FLEXIO0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - FLEXIO0.

AHB Clock Control 0 - FLEXIO0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_FLEXPWM0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - FLEXPWM0.

AHB Clock Control 0 - FLEXPWM0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_FLEXPWM1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - FLEXPWM1.

AHB Clock Control 0 - FLEXPWM1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_FMC()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - FMC.

AHB Clock Control 0 - FMC

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_FREQME()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - FREQME.

AHB Clock Control 0 - FREQME

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_I3C0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - I3C0.

AHB Clock Control 0 - I3C0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_INPUTMUX0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - INPUTMUX0.

AHB Clock Control 0 - INPUTMUX0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPI2C0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPI2C0.

AHB Clock Control 0 - LPI2C0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPI2C1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPI2C1.

AHB Clock Control 0 - LPI2C1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPSPI0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPSPI0.

AHB Clock Control 0 - LPSPI0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPSPI1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPSPI1.

AHB Clock Control 0 - LPSPI1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPUART0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPUART0.

AHB Clock Control 0 - LPUART0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPUART1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPUART1.

AHB Clock Control 0 - LPUART1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPUART2()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPUART2.

AHB Clock Control 0 - LPUART2

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPUART3()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPUART3.

AHB Clock Control 0 - LPUART3

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_LPUART4()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - LPUART4.

AHB Clock Control 0 - LPUART4

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_QDC0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - QDC0.

AHB Clock Control 0 - QDC0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_QDC1()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - QDC1.

AHB Clock Control 0 - QDC1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_SET_DATA()

|

inlinestaticconstexpr |

MRCC_GLB_CC0_SET - DATA.

AHB Clock Control Set 0 - Data array value, refer to corresponding position in MRCC_GLB_CCn.

◆ GLB_CC0_USB0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - USB0.

AHB Clock Control 0 - USB0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_UTICK0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - UTICK0.

AHB Clock Control 0 - UTICK0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC0_WWDT0()

|

inlinestaticconstexpr |

MRCC_GLB_CC0 - WWDT0.

AHB Clock Control 0 - WWDT0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_ADC0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - ADC0.

AHB Clock Control 1 - ADC0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_ADC1()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - ADC1.

AHB Clock Control 1 - ADC1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_CMP0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - CMP0.

AHB Clock Control 1 - CMP0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_CMP1()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - CMP1.

AHB Clock Control 1 - CMP1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_DAC0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - DAC0.

AHB Clock Control 1 - DAC0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_FLEXCAN0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - FLEXCAN0.

AHB Clock Control 1 - FLEXCAN0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_GPIO0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - GPIO0.

AHB Clock Control 1 - GPIO0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_GPIO1()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - GPIO1.

AHB Clock Control 1 - GPIO1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_GPIO2()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - GPIO2.

AHB Clock Control 1 - GPIO2

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_GPIO3()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - GPIO3.

AHB Clock Control 1 - GPIO3

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_GPIO4()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - GPIO4.

AHB Clock Control 1 - GPIO4

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_LPI2C2()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - LPI2C2.

AHB Clock Control 1 - LPI2C2

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_LPI2C3()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - LPI2C3.

AHB Clock Control 1 - LPI2C3

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_OPAMP0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - OPAMP0.

AHB Clock Control 1 - OPAMP0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_OSTIMER0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - OSTIMER0.

AHB Clock Control 1 - OSTIMER0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_PORT0()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - PORT0.

AHB Clock Control 1 - PORT0

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_PORT1()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - PORT1.

AHB Clock Control 1

AHB Clock Control 1 - PORT1

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_PORT2()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - PORT2.

AHB Clock Control 1 - PORT2

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_PORT3()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - PORT3.

AHB Clock Control 1 - PORT3

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_PORT4()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - PORT4.

AHB Clock Control 1 - PORT4

- [0b0]Peripheral clock is disabled

- [0b1]Peripheral clock is enabled

◆ GLB_CC1_RAMA()

|

inlinestaticconstexpr |

MRCC_GLB_CC1 - RAMA.

AHB Clock Control 1 - RAMA