|

mFrame

|

|

mFrame

|

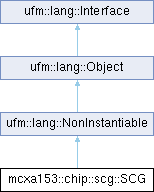

MCXA153 系統時脈產生器 (SCG) 控制介面 更多...

#include <SCG.h>

靜態公開方法(Static Public Methods) | |

| static constexpr uint32 | VERID_VERSION (uint32 value) |

| VERID - VERSION. | |

| static constexpr uint32 | PARAM_SOSCCLKPRES (uint32 value) |

| PARAM - SOSCCLKPRES. | |

| static constexpr uint32 | PARAM_SIRCCLKPRES (uint32 value) |

| PARAM - SIRCCLKPRES. | |

| static constexpr uint32 | PARAM_FIRCCLKPRES (uint32 value) |

| PARAM - FIRCCLKPRES. | |

| static constexpr uint32 | PARAM_ROSCCLKPRES (uint32 value) |

| PARAM - ROSCCLKPRES. | |

| static constexpr uint32 | TRIM_LOCK_TRIM_UNLOCK (uint32 value) |

| PARAM - TRIM_UNLOCK. | |

| static constexpr uint32 | TRIM_LOCK_IFR_DISABLE (uint32 value) |

| TRIM_LOCK - IFR_DISABLE. | |

| static constexpr uint32 | TRIM_LOCK_TRIM_LOCK_KEY (uint32 value) |

| TRIM_LOCK - TRIM_LOCK_KEY. | |

| static constexpr uint32 | CSR_SCS (uint32 value) |

| SCS. | |

| static constexpr uint32 | RCCR_SCS (uint32 value) |

| CSR - SCS. | |

| static constexpr uint32 | SOSCCSR_SOSCEN (uint32 value) |

| RCCR - SOSCEN. | |

| static constexpr uint32 | SOSCCSR_SOSCSTEN (uint32 value) |

| SOSCCSR - SOSCSTEN. | |

| static constexpr uint32 | SOSCCSR_SOSCCM (uint32 value) |

| SOSCCSR - SOSCCM. | |

| static constexpr uint32 | SOSCCSR_SOSCCMRE (uint32 value) |

| SOSCCSR - SOSCCMRE. | |

| static constexpr uint32 | SOSCCSR_LK (uint32 value) |

| SOSCCSR - LK. | |

| static constexpr uint32 | SOSCCSR_SOSCVLD (uint32 value) |

| SOSCVLD. | |

| static constexpr uint32 | SOSCCSR_SOSCSEL (uint32 value) |

| SOSCCSR - SOSCSEL. | |

| static constexpr uint32 | SOSCCSR_SOSCERR (uint32 value) |

| SOSCCSR - SOSCERR. | |

| static constexpr uint32 | SOSCCSR_SOSCVLD_IE (uint32 value) |

| SOSCCSR - SOSCVLD_IE. | |

| static constexpr uint32 | SOSCCFG_EREFS (uint32 value) |

| SOSCCFG - EREFS. | |

| static constexpr uint32 | SOSCCFG_RANGE (uint32 value) |

| SOSCCFG - RANGE. | |

| static constexpr uint32 | SIRCCSR_SIRCSTEN (uint32 value) |

| SIRCCSR - SIRCSTEN. | |

| static constexpr uint32 | SIRCCSR_SIRC_CLK_PERIPH_EN (uint32 value) |

| SIRCCSR - SIRC_CLK_PERIPH_EN. | |

| static constexpr uint32 | SIRCCSR_SIRCTREN (uint32 value) |

| SIRCCSR - SIRCTREN. | |

| static constexpr uint32 | SIRCCSR_SIRCTRUP (uint32 value) |

| SIRCTRUP. | |

| static constexpr uint32 | SIRCCSR_TRIM_LOCK (uint32 value) |

| SIRCCSR - TRIM_LOCK. | |

| static constexpr uint32 | SIRCCSR_COARSE_TRIM_BYPASS (uint32 value) |

| SIRCCSR - COARSE_TRIM_BYPASS. | |

| static constexpr uint32 | SIRCCSR_LK (uint32 value) |

| SIRCCSR - LK. | |

| static constexpr uint32 | SIRCCSR_SIRCVLD (uint32 value) |

| SIRCCSR - SIRCVLD. | |

| static constexpr uint32 | SIRCCSR_SIRCSEL (uint32 value) |

| SIRCCSR - SIRCSEL. | |

| static constexpr uint32 | SIRCCSR_SIRCERR (uint32 value) |

| SIRCCSR - SIRCERR. | |

| static constexpr uint32 | SIRCCSR_SIRCERR_IE (uint32 value) |

| SIRCCSR - SIRCERR_IE. | |

| static constexpr uint32 | SIRCTCFG_TRIMSRC (uint32 value) |

| SIRCTCFG - TRIMSRC. | |

| static constexpr uint32 | SIRCTCFG_TRIMDIV (uint32 value) |

| SIRCTCFG - TRIMDIV. | |

| static constexpr uint32 | SIRCTRIM_CCOTRIM (uint32 value) |

| SIRCTRIM - CCOTRIM. | |

| static constexpr uint32 | SIRCTRIM_CLTRIM (uint32 value) |

| SIRCTRIM - CLTRIM. | |

| static constexpr uint32 | SIRCTRIM_TCTRIM (uint32 value) |

| SIRCTRIM - TCTRIM. | |

| static constexpr uint32 | SIRCTRIM_FVCHTRIM (uint32 value) |

| SIRCTRIM - FVCHTRIM. | |

| static constexpr uint32 | SIRCSTAT_CCOTRIM (uint32 value) |

| SIRCSTAT - CCOTRIM. | |

| static constexpr uint32 | SIRCSTAT_CLTRIM (uint32 value) |

| SIRCSTAT - CLTRIM. | |

| static constexpr uint32 | FIRCCSR_FIRCEN (uint32 value) |

| FIRCEN. | |

| static constexpr uint32 | FIRCCSR_FIRCSTEN (uint32 value) |

| FIRCCSR - FIRCSTEN. | |

| static constexpr uint32 | FIRCCSR_FIRC_SCLK_PERIPH_EN (uint32 value) |

| FIRCCSR - FIRC_SCLK_PERIPH_EN. | |

| static constexpr uint32 | FIRCCSR_FIRC_FCLK_PERIPH_EN (uint32 value) |

| FIRCCSR - FIRC_FCLK_PERIPH_EN. | |

| static constexpr uint32 | FIRCCSR_FIRCTREN (uint32 value) |

| FIRCCSR - FIRCTREN. | |

| static constexpr uint32 | FIRCCSR_FIRCTRUP (uint32 value) |

| FIRCCSR - FIRCTRUP. | |

| static constexpr uint32 | FIRCCSR_TRIM_LOCK (uint32 value) |

| FIRCCSR - TRIM_LOCK. | |

| static constexpr uint32 | FIRCCSR_COARSE_TRIM_BYPASS (uint32 value) |

| FIRCCSR - COARSE_TRIM_BYPASS. | |

| static constexpr uint32 | FIRCCSR_LK (uint32 value) |

| FIRCCSR - LK. | |

| static constexpr uint32 | FIRCCSR_FIRCVLD (uint32 value) |

| FIRCCSR - FIRCVLD. | |

| static constexpr uint32 | FIRCCSR_FIRCSEL (uint32 value) |

| FIRCCSR - FIRCSEL. | |

| static constexpr uint32 | FIRCCSR_FIRCERR (uint32 value) |

| FIRCCSR - FIRCERR. | |

| static constexpr uint32 | FIRCCSR_FIRCERR_IE (uint32 value) |

| FIRCCSR - FIRCERR_IE. | |

| static constexpr uint32 | FIRCCSR_FIRCACC_IE (uint32 value) |

| FIRCCSR - FIRCACC_IE. | |

| static constexpr uint32 | FIRCCSR_FIRCACC (uint32 value) |

| FIRCCSR - FIRCACC. | |

| static constexpr uint32 | FIRCCFG_FREQ_SEL (uint32 value) |

| FIRCCFG - FREQ_SEL. | |

| static constexpr uint32 | FIRCTCFG_TRIMSRC (uint32 value) |

| FIRCCFG - TRIMSRC. | |

| static constexpr uint32 | FIRCTCFG_TRIMDIV (uint32 value) |

| FIRCCFG - TRIMDIV. | |

| static constexpr uint32 | FIRCTRIM_TRIMFINE (uint32 value) |

| FIRCTRIM - TRIMFINE. | |

| static constexpr uint32 | FIRCTRIM_TRIMCOAR (uint32 value) |

| FIRCTRIM - TRIMCOAR. | |

| static constexpr uint32 | FIRCTRIM_TRIMTEMP2 (uint32 value) |

| FIRCTRIM - TRIMTEMP2. | |

| static constexpr uint32 | FIRCTRIM_TRIMSTART (uint32 value) |

| FIRCTRIM - TRIMSTART. | |

| static constexpr uint32 | FIRCSTAT_TRIMFINE (uint32 value) |

| FIRCSTAT - TRIMFINE. | |

| static constexpr uint32 | FIRCSTAT_TRIMCOAR (uint32 value) |

| FIRCSTAT - TRIMCOAR. | |

| static constexpr uint32 | FIRCATC1_IDEALC (uint32 value) |

| FIRCATC1 - IDEALC. | |

| static constexpr uint32 | FIRCATC2_COARMINC (uint32 value) |

| FIRCATC2 - COARMINC. | |

| static constexpr uint32 | FIRCATC2_COARMAXC (uint32 value) |

| FIRCATC2 - COARMAXC. | |

| static constexpr uint32 | FIRCATC3_FINEMINC (uint32 value) |

| FIRCATC3 - FINEMINC. | |

| static constexpr uint32 | FIRCATC3_FINEMAXC (uint32 value) |

| FIRCATC3 - FINEMAXC. | |

| static constexpr uint32 | ROSCCSR_LK (uint32 value) |

| ROSCCSR - LK. | |

| static constexpr uint32 | ROSCCSR_ROSCVLD (uint32 value) |

| ROSCCSR - ROSCVLD. | |

| static constexpr uint32 | ROSCCSR_ROSCSEL (uint32 value) |

| ROSCCSR - ROSCSEL. | |

| static constexpr uint32 | ROSCCSR_ROSCERR (uint32 value) |

| ROSCCSR - ROSCERR. | |

保護方法(Protected Methods) | |

| virtual | ~SCG (void) override |

| Destroy the object. | |

保護方法(Protected Methods) 繼承自 ufm::lang::NonInstantiable 保護方法(Protected Methods) 繼承自 ufm::lang::NonInstantiable | |

| NonInstantiable (void)=delete | |

| 禁止實例化 NonInstantiable 類別 | |

| NonInstantiable (const NonInstantiable &)=delete | |

| 禁止複製建構函式 | |

| virtual | ~NonInstantiable (void) override=default |

| Destroy the Non Instantiable object. | |

| NonInstantiable & | operator= (const NonInstantiable &)=delete |

| NonInstantiable & | operator= (NonInstantiable &&)=delete |

額外的繼承成員 | |

公開方法(Public Methods) 繼承自 ufm::lang::Object 公開方法(Public Methods) 繼承自 ufm::lang::Object | |

| void * | operator new (size_t n) |

| 使用運算子 new 分配記憶體 | |

| void * | operator new (size_t n, void *p) |

| 在指定記憶體上調用運算子 new | |

| virtual ufm::lang::Object & | getObject (void) override |

| 取得對應的 Object 物件 | |

| void | delay (int milliseconds) const |

| 延遲指定的毫秒數進行執行緒等待 | |

| bool | equals (Object *object) const |

| 判斷與另一物件是否為相同參照(指標型態比較) | |

| bool | equals (Object &object) const |

| 判斷與另一物件是否為相同參照(參照型態比較) | |

| void | wait (void) const |

| 使當前線程等待直到被通知 | |

| bool | wait (int timeout) const |

| 等待通知或超時 | |

| bool | yield (void) const |

| 讓執行緒讓渡控制權給同優先權的下一個執行緒 | |

| int | lock (void) const |

| 核心鎖定,鎖定期間禁止線程切換 | |

| int | unlock (void) const |

| 核心解鎖 | |

| ufm::sys::Thread * | currentThread (void) const |

| 取得當前執行緒指標 | |

| virtual int | hashcode (void) const |

| 返回對象的哈希碼值。支持這種方法是為了散列表,如HashMap提供的那樣。 | |

公開方法(Public Methods) 繼承自 ufm::lang::Interface 公開方法(Public Methods) 繼承自 ufm::lang::Interface | |

| virtual | ~Interface (void)=default |

| 虛擬析構函式 | |

MCXA153 系統時脈產生器 (SCG) 控制介面

SCG類別提供MCXA153系統時脈產生與管理的全面控制功能。包括多重時脈源配置、 系統時脈選擇、時脈監控、自動調校功能以及電源管理特性。

主要功能特色:

時脈源詳細說明:

使用範例:

|

inlinestaticconstexpr |

SCS.

System Clock Source

|

inlinestaticconstexpr |

FIRCATC1 - IDEALC.

FIRC Auto-trimming Counter 1 - Ideal Counter

|

inlinestaticconstexpr |

FIRCATC2 - COARMAXC.

FIRC Auto-trimming Counter 1 - Coarse Trim Maximum Counter

|

inlinestaticconstexpr |

FIRCATC2 - COARMINC.

FIRC Auto-trimming Counter 1 - Coarse Trim Minimum Counter

|

inlinestaticconstexpr |

FIRCATC3 - FINEMAXC.

FIRC Auto-trimming Counter 2 - Fine Trim Maximum Counter

|

inlinestaticconstexpr |

FIRCATC3 - FINEMINC.

FIRC Auto-trimming Counter 2 - Fine Trim Minimum Counter

|

inlinestaticconstexpr |

FIRCCFG - FREQ_SEL.

FIRC Configuration Register - Frequency select

|

inlinestaticconstexpr |

FIRCCSR - COARSE_TRIM_BYPASS.

FIRC Control Status Register - Coarse Auto Trim Bypass

|

inlinestaticconstexpr |

FIRCCSR - FIRC_FCLK_PERIPH_EN.

FIRC Control Status Register - FRO_HF Clock to peripherals Enable

[0b0]FRO_HF to peripherals is disabled

[0b1]FRO_HF to peripherals is enabled

|

inlinestaticconstexpr |

FIRCCSR - FIRC_SCLK_PERIPH_EN.

FIRC Control Status Register - FIRC 48 MHz Clock to peripherals Enable

[0b0]FIRC 48 MHz to peripherals is disabled

[0b1]FIRC 48 MHz to peripherals is enabled

|

inlinestaticconstexpr |

FIRCCSR - FIRCACC.

FIRC Control Status Register - FIRC Frequency Accurate

-[0b0]FIRC is not enabled or clock is not accurate.

-[0b1]FIRC is enabled and output clock is accurate after some preparation time which is obtained by counting FRO_HF clock.

|

inlinestaticconstexpr |

FIRCCSR - FIRCACC_IE.

FIRC Control Status Register - FIRC Accurate Interrupt Enable

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

FIRCCSR - FIRCERR.

FIRC Control Status Register - FIRC Clock Error

|

inlinestaticconstexpr |

FIRCCSR - FIRCERR_IE.

FIRC Control Status Register - FIRC Clock Error Interrupt Enable

|

inlinestaticconstexpr |

FIRCCSR - FIRCSEL.

FIRC Control Status Register - FIRC Selected

|

inlinestaticconstexpr |

FIRCCSR - FIRCSTEN.

FIRC Control Status Register - FIRC Stop Enable

|

inlinestaticconstexpr |

FIRCCSR - FIRCTREN.

FIRC Control Status Register - FRO_HF Trim Enable

|

inlinestaticconstexpr |

FIRCCSR - FIRCTRUP.

FIRC Control Status Register - FIRC Trim Update

|

inlinestaticconstexpr |

FIRCCSR - FIRCVLD.

FIRC Control Status Register - FIRC Valid status

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

FIRCCSR - TRIM_LOCK.

FIRC Control Status Register - FIRC TRIM LOCK

|

inlinestaticconstexpr |

FIRCSTAT - TRIMCOAR.

FIRC Auto-trimming Status Register - Trim Coarse

|

inlinestaticconstexpr |

FIRCSTAT - TRIMFINE.

FIRC Auto-trimming Status Register - Trim Fine

|

inlinestaticconstexpr |

FIRCCFG - TRIMDIV.

FIRC Configuration Register - FIRC Trim Pre-divider

|

inlinestaticconstexpr |

FIRCCFG - TRIMSRC.

FIRC Configuration Register - Trim Source

|

inlinestaticconstexpr |

FIRCTRIM - TRIMCOAR.

FIRC Trim Register - Trim Coarse

|

inlinestaticconstexpr |

FIRCTRIM - TRIMFINE.

FIRC Trim Register - Trim Fine

|

inlinestaticconstexpr |

FIRCTRIM - TRIMSTART.

FIRC Trim Register - Trim Start

|

inlinestaticconstexpr |

FIRCTRIM - TRIMTEMP2.

FIRC Trim Register - Trim Temperature2

|

inlinestaticconstexpr |

PARAM - FIRCCLKPRES.

Parameter Register - FIRC Clock Present

|

inlinestaticconstexpr |

PARAM - ROSCCLKPRES.

Parameter Register - ROSC Clock Present

|

inlinestaticconstexpr |

PARAM - SIRCCLKPRES.

Parameter Register - SIRC Clock Present

|

inlinestaticconstexpr |

PARAM - SOSCCLKPRES.

Parameter Register - SOSC Clock Present

|

inlinestaticconstexpr |

CSR - SCS.

Clock Status Register - System Clock Source

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

ROSCCSR - ROSCERR.

ROSC Control Status Register - ROSC Clock Error

|

inlinestaticconstexpr |

ROSCCSR - ROSCSEL.

ROSC Control Status Register - ROSC Selected

|

inlinestaticconstexpr |

ROSCCSR - ROSCVLD.

ROSC Control Status Register - ROSC Valid

|

inlinestaticconstexpr |

SIRCCSR - COARSE_TRIM_BYPASS.

SIRC Control Status Register - Coarse Auto Trim Bypass

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

SIRCCSR - SIRC_CLK_PERIPH_EN.

SIRC Control Status Register - SIRC Clock to Peripherals Enable

|

inlinestaticconstexpr |

SIRCCSR - SIRCERR.

SIRC Control Status Register - SIRC Clock Error

|

inlinestaticconstexpr |

SIRCCSR - SIRCERR_IE.

SIRC Control Status Register - SIRC Clock Error Interrupt Enable

|

inlinestaticconstexpr |

SIRCCSR - SIRCSEL.

SIRC Control Status Register - SIRC Selected

|

inlinestaticconstexpr |

SIRCCSR - SIRCSTEN.

SIRC Control Status Register - SIRC Stop Enable

|

inlinestaticconstexpr |

SIRCCSR - SIRCTREN.

SIRC Control Status Register - SIRC 12 MHz Trim Enable (SIRCCFG[RANGE]=1)

|

inlinestaticconstexpr |

SIRCTRUP.

SIRC Control Status Register - SIRC Trim Update

|

inlinestaticconstexpr |

SIRCCSR - SIRCVLD.

SIRC Control Status Register - SIRC Valid

|

inlinestaticconstexpr |

SIRCCSR - TRIM_LOCK.

SIRC Control Status Register - SIRC TRIM LOCK

|

inlinestaticconstexpr |

SIRCSTAT - CCOTRIM.

SIRC Trim Register - CCO Trim

|

inlinestaticconstexpr |

SIRCSTAT - CLTRIM.

SIRC Auto-trimming Status Register - CL Trim

|

inlinestaticconstexpr |

SIRCTCFG - TRIMDIV.

SIRC Trim Configuration Register - SIRC Trim Pre-divider

|

inlinestaticconstexpr |

SIRCTCFG - TRIMSRC.

SIRC Trim Configuration Register - Trim Source

|

inlinestaticconstexpr |

SIRCTRIM - CCOTRIM.

SIRC Trim Register - CCO Trim

|

inlinestaticconstexpr |

SIRCTRIM - CLTRIM.

SIRC Trim Register - CL Trim

|

inlinestaticconstexpr |

SIRCTRIM - FVCHTRIM.

SIRC Trim Register

|

inlinestaticconstexpr |

SIRCTRIM - TCTRIM.

SIRC Trim Register - Trim Temp

|

inlinestaticconstexpr |

SOSCCFG - EREFS.

SOSC Configuration Register - External Reference Select

|

inlinestaticconstexpr |

SOSCCFG - RANGE.

SOSC Configuration Register - SOSC Range Select

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

SOSCCSR - SOSCCM.

SOSC Control Status Register - SOSC Clock Monitor Enable

|

inlinestaticconstexpr |

SOSCCSR - SOSCCMRE.

SOSC Control Status Register - SOSC Clock Monitor Reset Enable

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

SOSCCSR - SOSCERR.

SOSC Control Status Register - SOSC Clock Error

-[0b0]SOSC Clock Monitor is disabled or has not detected an error

-[0b1]SOSC Clock Monitor is enabled and detected an error

|

inlinestaticconstexpr |

SOSCCSR - SOSCSEL.

SOSC Control Status Register - SOSC Selected

|

inlinestaticconstexpr |

SOSCCSR - SOSCSTEN.

SOSC Control Status Register - SOSC Stop Enable

[0b0]SOSC is disabled in Deep Sleep mode

[0b1]SOSC is enabled in Deep Sleep mode only if SOSCEN is set

|

inlinestaticconstexpr |

SOSCVLD.

SOSC Control Status Register - SOSC Valid

|

inlinestaticconstexpr |

SOSCCSR - SOSCVLD_IE.

SOSC Control Status Register - SOSC Valid Interrupt Enable

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |

TRIM_LOCK - TRIM_LOCK_KEY.

Trim Lock register - TRIM_LOCK_KEY

|

inlinestaticconstexpr |

|

inlinestaticconstexpr |